4.7. Système des interruptions du 8086

Le microprocesseur 8086 peut gérer jusqu’à 256 interruptions :

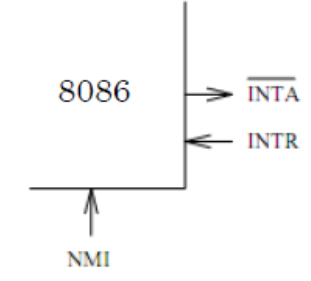

- Les interruptions matérielles sont produites par l’activation des lignes INTR et NMI du processeur

- Les interruptions logicielles sont produites par l’instruction INT n, où n est le type de l’interruption

- Les déroutements sont générés par le processeur

- NMI est utilisée pour envoyer au processeur une interruption non masquable (NMI, Non Maskable Interrupt). Le processeur ne peut pas ignorer ce signal, et va la traiter immédiatement. Ce signal est normalement utilisé pour détecter des erreurs matérielles (mémoire principale défaillante par exemple)

- INTR (Interrupt Request), est utilisé pour indiquer l’arrivée masquable.

- INTA (Interrupt Acknowledge) si la demande

d’interruption reçue sur INTR est acceptée, le processeur envoi

l’acquittement (confirmation d’acceptation) de cette demande d’interruption sur

cette ligne en injectant un 0). Cela permet aux périphériques de savoir si leur

demande.

A un instant donné, les interruptions INTR sont soit masquées soit autorisées, suivant l’état de l’indicateur IF (Interrupt Flag) du registre d’état :

- Si IF = 1, le processeur accepte les demandes d’interruptions INTR, c’est à dire qu’il les traite immédiatement ;

- Si IF = 0, le processeur ignore ces interruptions.

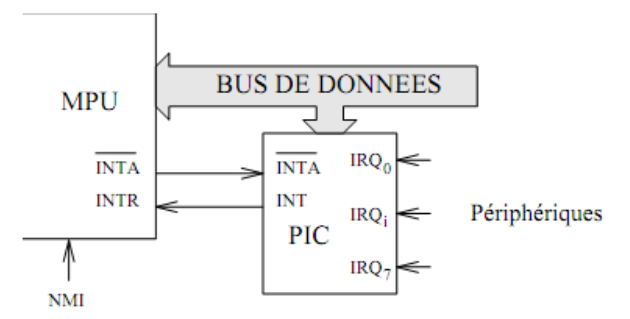

Le contrôleur d’interruptions (PIC) est relié aux interfaces gérant les périphériques par les bornes IRQ (InteRrupt reQuest).

- Il gère les demandes d’interruption envoyées par les périphériques, de façon à les envoyer une par une au processeur (via INTR).

- Il est possible de programmer le contrôleur pour affecter des priorités différentes à chaque périphérique.

- Avant d’envoyer l’interruption suivante, le contrôleur attend d’avoir reçu le signal INTA, indiquant que le processeur a bien traité l’interruption en cours.

Déroulement d’une interruption externe masquable:

- Un signal INT est émis par un périphérique (ou plutôt par l’interface gérant celui-ci).

- Le contrôleur d’interruptions reçoit ce signal sur une de ses bornes IRQi. Dès que cela est possible (suivant les autres interruptions en attente de traitement), le contrôleur envoie un signal sur sa borne INT.

- Le processeur prend en compte le signal sur sa borne INTR après avoir achevé l’exécution de l’instruction en cours (ce qui peut prendre quelques cycles d’horloge). Si l’indicateur IF=0, le signal est ignoré, sinon, la demande d’interruption est acceptée.

- Si la demande est acceptée, le MPU met sa sortie INTA au niveau 0 pendant 2 cycles d’horloge, pour indiquer au contrôleur qu’il prend en compte sa demande.

- En réponse, le contrôleur d’interruption place le numéro de l’interruption associé à la borne IRQi sur le bus de données.

- Le processeur lit

le numéro de l’interruption sur le bus de données et l’utilise pour trouver le

vecteur d’interruption. Ensuite:

- sauvegarde les indicateurs du registre d’état sur la pile ;

- met l’indicateur IF à 0 (masque les interruptions suivantes) ;

- sauvegarde CS et IP sur la pile ;

- cherche dans la table des vecteurs d’interruptions l’adresse du traitant d’interruption, qu’il charge dans CS:IP.

- La procédure traitant l’interruption se déroule. Pendant ce temps, les interruptions sont masquées (IF=0). Si le traitement est long, on peut dans certains cas ré-autoriser les interruptions avec l’instruction STI (positionner IF à 1).

- La procédure se termine par l’instruction IRET, qui restaure CS, IP et les indicateurs à partir de la pile, ce qui permet de reprendre le programme qui avait été interrompu.

آخر تعديل: الخميس، 30 نوفمبر 2023، 7:05 PM