Introduction

Quelques définitions.

Bus = ensemble de liaisons physiques pouvant être exploitées en commun par plusieurs éléments matériels afin de communiquer.

Bande passante = débit d’informations ; quantité d’informations échangée par unité de temps.

Latence = Temps de réponse du bus à une requête de transfert, temps minimum d’établissement

de la connexion : indépendant de la quantité de données à transporter.

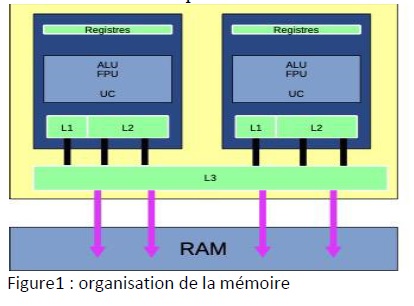

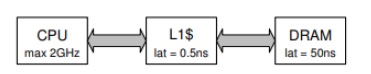

Principe de fonctionnement : le CPU a besoin d’un débit soutenu en lecture d’instructions et de données (figure 1).

Problème : la RAM qui stocke ces instructions et données est beaucoup trop lente pour assurer ce débit.

Solutions : Hiérarchie mémoire et principe de localité mémoire

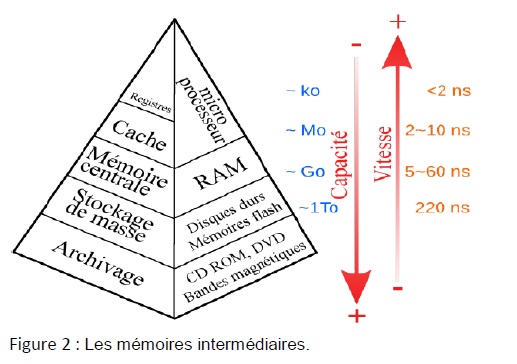

Hiérarchie mémoire

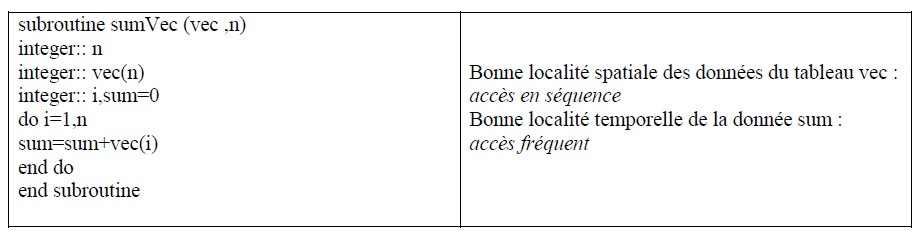

Utilisation de mémoires intermédiaires (figure 2) entre la RAM et le CPU, permet de stocker les données utiles au plus proche du CPU comme suit :

1) Les registres qui appartiennent au CPU.

- Extrêmement rapides,

- Fonctionnent à la vitesse des CPU

- Capacité très minimale: qq Ko

2) La mémoire cache (L1, L2, L3)

- Très rapides

- Mettent à disposition du CPU les copies de quelques données et instructions prises dans la mémoire centrale.

- Capacité: qq Ko _ 128 Mo

La cache L1 est le plus rapide mais de taille plus restreinte.

3) La RAM/mémoire centrale

-Vitesse de réaction est trop lente

- Les données y sont lues par blocs et mises à portée de main du CPU grâce à la mémoire cache.

Capacité: 1_ jusqu’à quelques To.

4) La Mémoire de masse : les disques (plusieurs dizaines de To)

1)Principe :

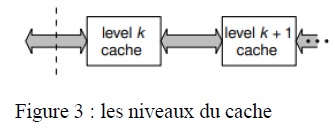

Lorsque le processeur tente d’accéder à une information (instruction ou donnée) du Kième niveau de cache (figure 3) :

Si l’information se trouve dans le cache (hit) «succès de cache» :

- Donnée renvoyée «aussitôt». - Pas besoin d’accéder aux niveaux suivants.

- Le processeur y accède sans état d’attente.

Si l’information ne s’y trouve pas (miss) «défaut de cache» :

- La requête transmise récursivement au niveau k + 1.

- Réponse mémorisée (au niveau k) et transmise au demandeur.

- Le cache est chargé avec un bloc d’informations de la mémoire.

- CPU en attente pendant ce temps.

2) Calcul du temps d’accès moyen

Le temps d’accès moyen à la mémoire AMAT-Average Memory Access Time au niveau k :

AMAT (k)=hit time + (miss rate x miss penalty) ou :

hit time : temps de réponse en cas de hit dans Lk ≈ Latence de la mémoire Lk

miss rate : pourcentage de cache miss au niveau k avec miss rate + hit rate =1.

miss penalty = Lat(k+1) : latence supplémentaire en cas de défaut de Lk.

La vitesse réelle CPU ≈ 1/AMAT .

Exemple soit la machine suivante :

CPU : max 2 Ghz ; lat(L1) = 0.5 ns ; DRAM lat =50 ns

Supposons 20 % miss rate AMAT(1)=0.5 ns + 20% x 50 ns=10.5 ns

La vitesse réelle CPU = 1/AMAT ≈ 100 Mhz.

Calculer AMAT si miss rate = 1% ? sol AMAT=1 ns et VR CPU =1/AMAT≈ 1 Ghz.

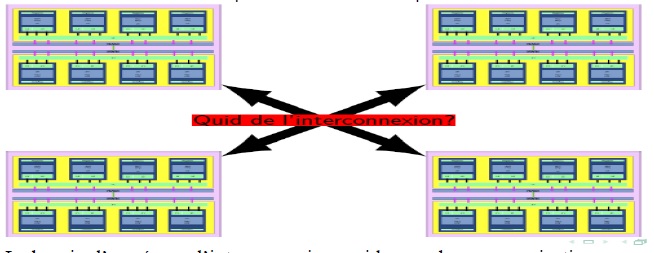

2- Le principe de localité mémoire

Les mémoires sont en général conçues pour exploiter les principes de localité mémoire :

L’exécution d’un programme accède à la mémoire de façon «localisée» dans le temps et dans l’espace.

Localité spatiale : lorsqu’un programme accède à une donnée ou à une instruction, il est probable qu’il accédera ensuite aux données ou instructions voisines.

Mise en cache dans les niveaux rapides de la hiérarchie

Localité temporelle : lorsqu’un programme accède à une donnée ou à une instruction, il est probable qu’il y accédera à nouveau dans un futur proche.

Mise en cache par blocs de plusieurs valeurs consécutives Remarque: doit être vidangé (cache flush) à chaque changement de contexte vers un nouveau processus.

Du processeur au noeud

Noeud = Ressource de calcul contenant plusieurs processeurs (socket) partageant une même mémoire

Temps d’accès à la mémoire partagée

Deux classes d’architectures parallèles à mémoire partagée différenciées par leur temps d’accès à la mémoire. :

1)UMA (Uniform Memory Access) Même temps d’accès à une zone mémoire, quel que soit le processeur ayant fait la requête.

Exemple : systèmes SMP (Symmetric MultiProcessing). Avantages Augmentation nombre de coeurs … accès concurrents. Inconvénients Encombrement …Perte d’efficacité.

2)NUMA (Non Uniform Memory Access) Temps d’accès à la mémoire dépend du processeur.

Exemple : Plusieurs blocs SMP inter-connectés.

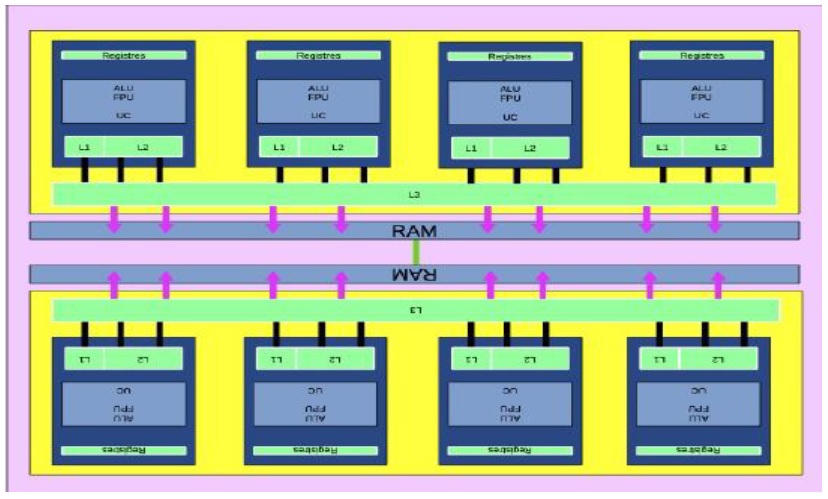

Cluster de calcul

Un cluster est un ensemble de plusieurs noeuds reliés par un réseau d’interconnexion.

-Le besoin d’un réseau d’interconnexion rapide pour les communications.

- Les noeuds sont stockés dans des racks.

-Chaque noeud est connecté à l’aide d’un switch sur le réseau -- Pas de mémoire partagée.

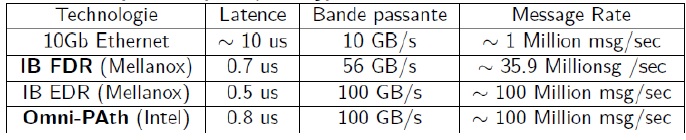

5-1 Caractéristiques des principaux types de réseau d’interconnexion