1.1.4. Mémoire Centrale (MC) ou Mémoire Principale (MP) : C'est la partie qui contient les programmes et les données qui seront exécutés par le Processeur. Le temps d’accès est y relativement faible (elle est réalisée à l’aide des semi-conducteurs ce qui la rend plus rapide que les mémoires magnétiques). La mémoire est divisée en emplacements de taille fixe (par exemple 8 bits) utilisés pour stocker instructions et données.

1.1.4.1. Organisation de la mémoire centrale

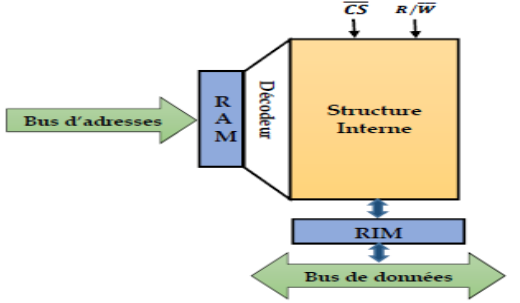

La figure ci-dessous schématise un circuit mémoire où l’on peut distinguer :

- RAM (Registre Adresse Mémoire) : ce registre stock l’adresse du mot à lire ou à écrire.

- RIM (Registre Information Mémoire) : stock l’information lu à partir de la mémoire ou l’information à écrire dans la mémoire.

- Décodeur : permet de sélectionner un mot mémoire.

- R/W: commande de lecture/écriture

- Bus d’adresses k bits

- Bus de données n bits

- CS: Signal sélection du circuit (Chip Select)

- Mémoire de 2k mots mémoires

Une mémoire centrale est formée de trois éléments essentiels : Les circuits de mémorisation (stockage), la logique d’adressage des mots et La logique d’entrée/sortie.

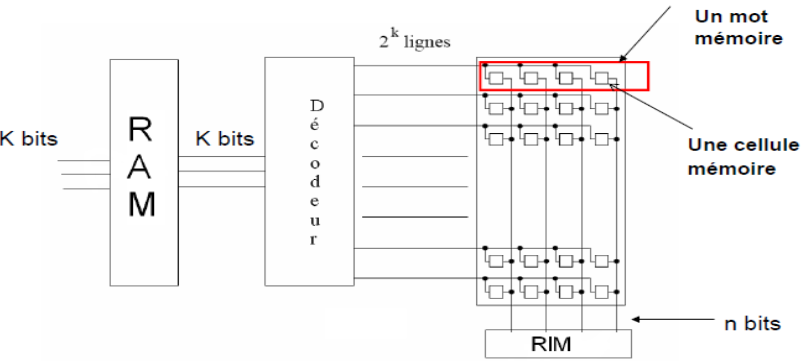

a-) Mémoire à une dimension

C’est l’organisation la plus simple. Un seul décodeur est nécessaire. Il a k bits en entrée et 2K lignes en sortie

Figure 1.2. Organisation des mémoires (RAM)

Comment calculer la capacité d’une MC ?

• Soit k la taille du bus d’adresses (taille du registre RAM)

• Soit n la taille du bus de données (taille du registre RIM ou la taille d’un mot mémoire )

On peut exprimer la capacité de la mémoire centrale soit en nombre de mots mémoire ou en bits (octets, KO, MO, ….). La capacité = 2k Mots mémoires = La capacité = 2k * n Bits

Exemple : Dans une mémoire la taille du bus d’adresses K=14 bits et la taille du bus de données n=4 bits. Calculer la capacité de cette mémoire ?

C=214 = 16384 Mots de 4 bits ou C= 214 * 4 = 65536 Bits = 8192 Octets = 8 Ko

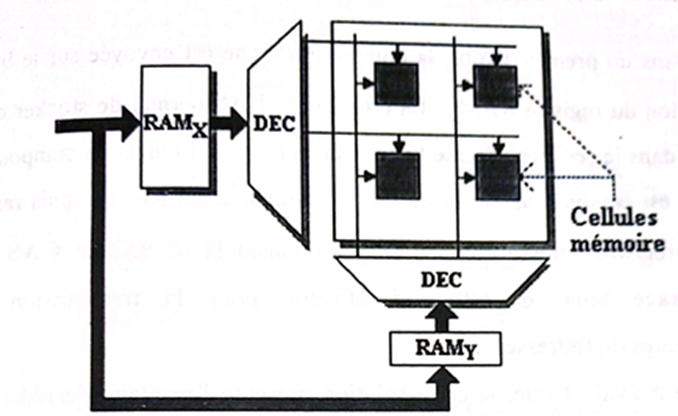

b-) Mémoire à deux dimensions

L’adresse de la mémoire est divisé en deux parties ligne et colonne. Deux registres d’adresses (RAMx et RAMy) sont donc nécessaires pour contenir les deux composants d’adresse. Une cellule est sélectionnée par l’intersection d’une sortie du décodeur lignes et d’une sortie du décodeur colonnes.

Figure 1.3. Sélection d’une cellule dans une mémoire à deux dimensions