4.6. Les systèmes hiérarchisés d’interruptions

Dans un ordinateur, les interruptions n’ont pas toutes le même degré d’urgence. Le traitement d’une interruption doit pouvoir être interrompu par une cause plus urgente, mais pas par une interruption de degré d’urgence inférieur ou égal. C’est la raison pour laquelle les interruptions sont classées per niveau de priorité tel que :

- Les interruptions appartenant à un même niveau soient affectées de la même priorité.

- Les interruptions de niveau de priorité inferieur ou égale au programme en exécution soient bloquées.

4.6.1 Inhibition, masquage et validation

Masquer et démasquer une interruption : Certaines interruptions présentent tellement d'importance qu'il ne doit pas être possible d'interrompre leur traitement. On masquera alors les autres interruptions pour empêcher leur prise en compte. Certaines interruptions sont non-masquables : on les prend obligatoirement en compte. Une interruption masquée n'est pas ignorée : elle est prise en compte dès qu'elle est démasquée.

Armer et Désarmer une interruption : Au contraire, une interruption peut être désarmée ou inhibée : elle sera ignorée et donc perdue. Par défaut, les interruptions sont évidemment armées.

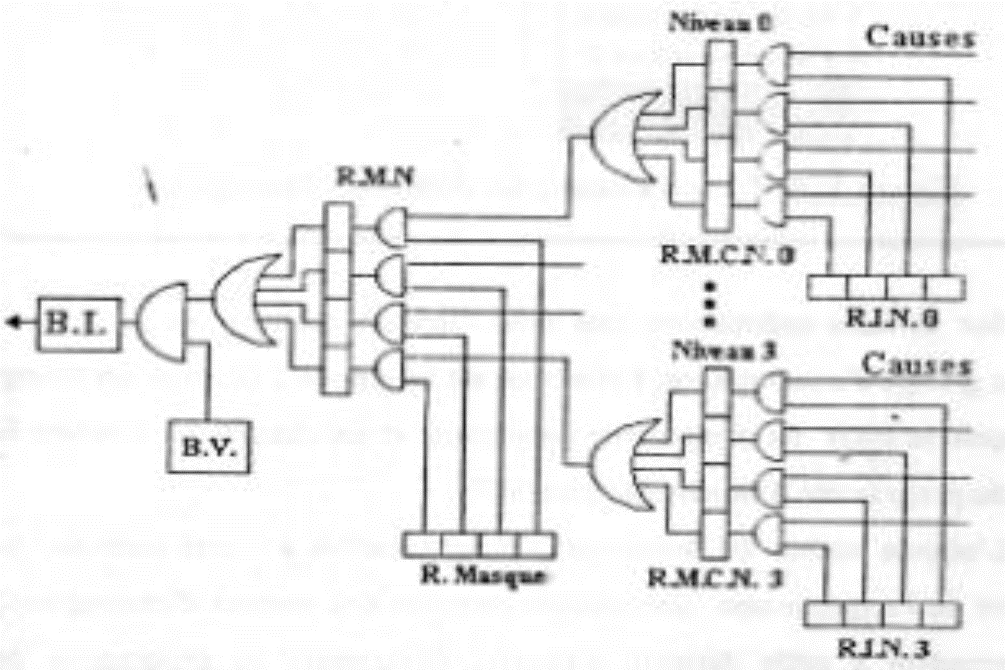

Un système d’interruptions hiérarchisées comporte les éléments suivants :

Figure 4.8 : Système d’IT à 4 niveaux

- Des registres d’inhibition (R.I.N.i) : à chaque niveau est associé un registre d’inhibition dans lequel une bascule est réservée pour chacune des causes de niveau (une interruption inhibée est perdu).

- Un registre masque (R.M.N) : à chaque niveau est associée une bascule dans ce registre. Masquer un niveau d’interruptions revient à le bloquer momentanément. Une interruption qui pourrait survenir alors que son niveau est masqué ne peut pas être immédiatement prise en compte, mais elle est mémorisée. Elle est prise en compte dès que son niveau est démasqué par une interruption appartement à un niveau non masqué.

- R.M.C.N.i : Registre de Mémorisation des Causes du Niveau i

- Une bascule de validation (BV) : permet de désactiver, lorsqu’elle est à « 0 » tout le système d’interruption. Les interruptions qui arrivent à CPU lorsque BV est à « 0 », ne sont pas perdues puisqu’elles sont mémorisées.

- Une bascule d’Interruption (BI) : qui indique la présence d’une interruption.

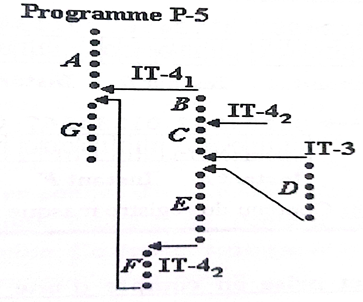

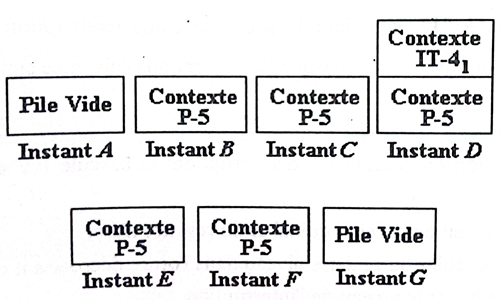

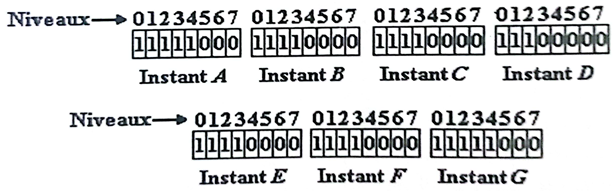

Exemple : Dans l’exemple de la figure 4.9.a., Le programme P de niveau 5 est interrompu par une interruption de niveau 4 (IT-41). Le contexte du programme P-5 est enregistré dans la pile. Au cours du traitement de l’interruption de niveau IT-4, il se produit une autre interruption de même niveau 4 (IT-42) qui n’est pas prise en compte, mais qui est mémorisée. L’interruption de niveau 3 (IT-3) qui survient juste après, est quand elle est prise en compte. Le contexte du programme du traitement de l’IT-41 est rangé dans la pile. A la fin du traitement de l’IT-3, le contexte du programme de l’IT-41 est restauré. L’exécution du programme de l’IT-41 reprend a partir de l’adresse indiqué par le compteur ordinal. Lorsque le contexte du programme P-5 est restauré, le niveau 4 n’est plus masqué. L’IT-42 est prise en compte et le contexte de p-5 est de nouveau rangé dans la pile. L’UC reprend l’exécution de p-5 à la fin du programme IT-42. Dans cet exemple la première restauration du contexte p-5 est unique.

Le retour obligatoire au programme interrompu peut être évité en tenant un registre des interruptions en attente d’être traitées. On recherchera dans ce registre l’interruption la plus prioritaire.

La figure 4.9.b, illustre l’état de la pile et la figure 4.9.c représente l’état du registre masque lors des différentes étapes de traitement de l’exemple.

Figure 4.9.a : Exemple d’enchaînement des signaux d’interruptions.

Figure 4.9.b : Contenu de la pile à chaque instant.

Figure 4.9.c : Contenu du registre masque à chaque instant.

4.6.2) Détection et prise en compte d’une interruption dans un système hiérarchisé

Lorsqu’elle arrive à un point interruptible, l’unité centrale teste l’état de la bascule BI. Si elle est à « 1 », signifiant la présence d’au moins une interruption appartenant à un niveau non masqué, les opérations suivantes sont réalisées :

- Désactivation du mécanisme d’interruption : la bascule BV est remise à « 0 »

- Sauvegarde du contexte du programme courant (conteur ordinal, du registre d’état, registres généraux nécessaires).

- Détermination du niveau de l’interruption : en testant les bascules du registre niveau (R.M.N) dans l’ordre décroissant des priorités.

- Masquage des niveaux les moins prioritaires : en positionnant à « 0 » des bascules du registre masque correspondant aux niveaux qui doivent être démasqués.

- Recherche de la cause de l’interruption : les bascules du registre de mémorisation des causes associé au niveau actif (R.M.C.N.i) sont testées dans un ordre qui définit la priorité entre les interruptions du niveau.

- Activation du mécanisme d’interruption : en remettant la bascule BV à 1 pour autoriser la prise en compte d’interruptions plus prioritaires

- Chargement du contexte de programme de traitement de l’interruption dans l’unité centrale. Ce dernier sauvegarde le registre masque et les registres qu’il est susceptibles de modifier.

- Traitement effectif de l’interruption

- Acquittement de l’interruption : un accusé de réception est adressé au périphérique source de l’interruption.

- Désactivation du système d’interruption (remise à « 0 » de BV)

- Restaurations des registres sauvegardés.

- Exécution de l’instruction de retour. Cette instruction a pour effet de restaurer le contenu des registres sauvegardés (compteur ordinal et registre d’état) du programme interrompu, et remettre à 1 la bascule BV.

4.6.3 Codage des niveaux

Les évènements qui peuvent provoquer une interruption, sont souvent top nombreuses pour que l’on puisse réserver une entrée à chacun d’entre eux au niveau de l’unité centrale. Les interruptions sont réparties comme dans le cas précédent au plusieurs niveaux regroupant chacun une ou plusieurs interruptions. Le numéro du niveau est adressé à l’UC l’lorsqu’il se produit une interruption appartenant à ce niveau.

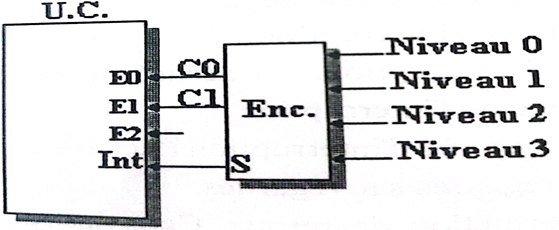

Figure 4.10 : Codage des niveaux d’IT

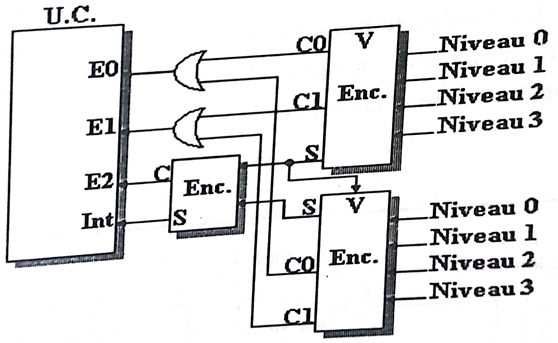

Il est possible de relié l’UC à un plus grand nombre de périphériques à l’aide d’encodeurs de priorité connectés en cascade.

Enc : Encodeur de priorité S : Sorties actives

Int : Interruption présente Ci : Code du niveau le plus prioritaire

Ei : Numéro du niveau le plus prioritaire

Figure 4.11 : Codage à plusieurs niveaux

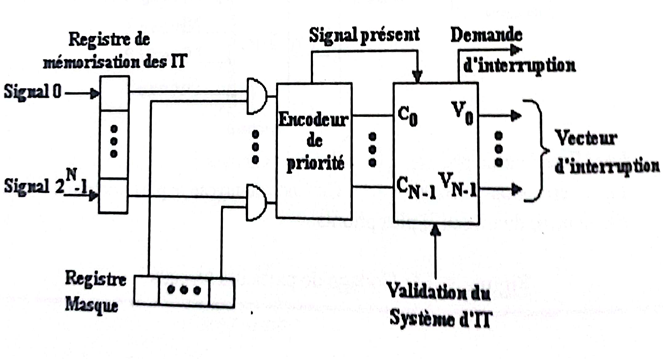

4.6.4) Interruptions vectorisées

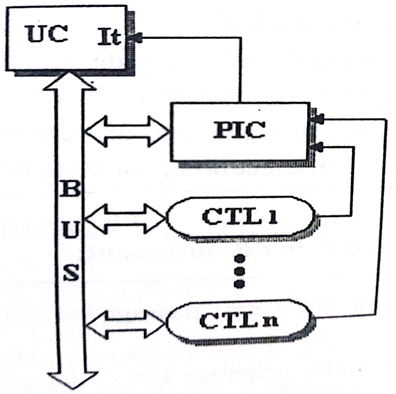

Les contrôleurs d’interruptions (ou PIC pour Priority Interrupt Coder) permettent d’accélérer le processus de reconnaissance de l’interruption. Si le niveau de l’interruption courante est plus prioritaire que le niveau du programme en cours d’exécution, une demande d’interruption est adressée à l’UC. Un encodeur de priorité indique le niveau de l’IT la plus prioritaire parmi celles qui ne sont pas masquées. Les sorties de l’encodeur permettent de sélectionner dans la mémoire du PIC le mot correspondant à l’interruption. Le contenu de ce mot est souvent appelé vecteur d’interruption.

Figure 4.12 : Schéma de principe d’un PIC

Figure 4.13 : Liaison avec un PIC