1.5.4 Structure du système cache/mémoire principale

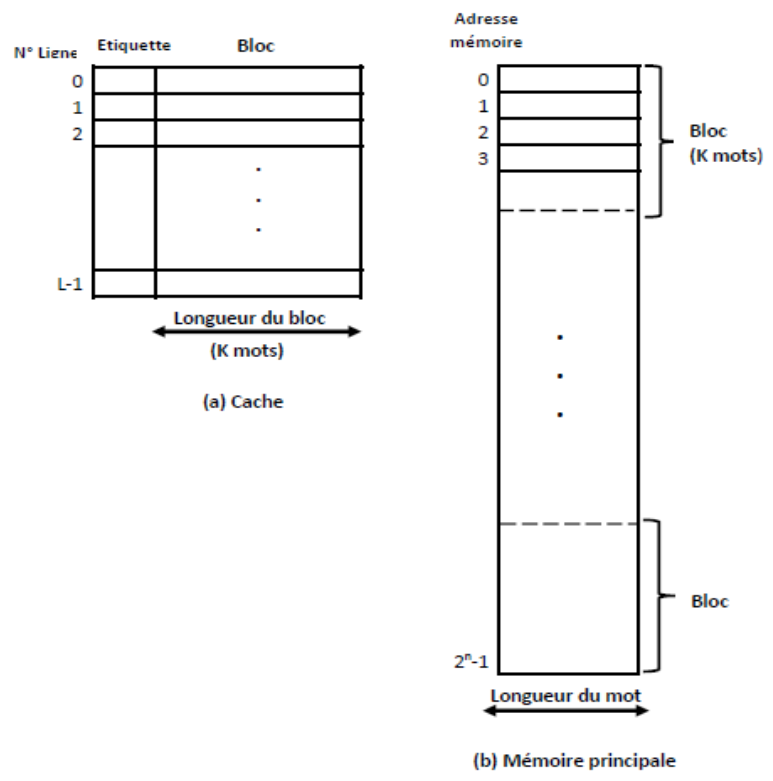

Les mémoires caches contiennent généralement un tableau d’étiquettes qui contient les adresses des données contenues dans le cache et un tableau de données qui contient les données elles-mêmes. La mémoire principale contient jusqu’à 2n mots adressables, chacun possédant une adresse unique de n bits. Pour la correspondance avec la mémoire cache, cette mémoire se compose de blocs d’une longueur fixe de K mots chacun. Autrement dit, il y a M = 2n/K blocs. Le cache se divise en L lignes de K mots.

La figure ci-dessous illustre la structure du système cache/mémoire principale.

Figure 1.23 : structure du système cache/mémoire principale

Modifié le: mardi 23 décembre 2025, 14:13