1.5.6 Méthodes d’accès aux caches

D’habitude le CPU utilise une adresse pour accéder à une information en MC, le principe est le même pour une mémoire cache sauf que la correspondance entre adresse de l’information en MC et celle en mémoire cache doit être calculée. Il existe trois techniques de correspondance : associative, directe et associative par ensemble.

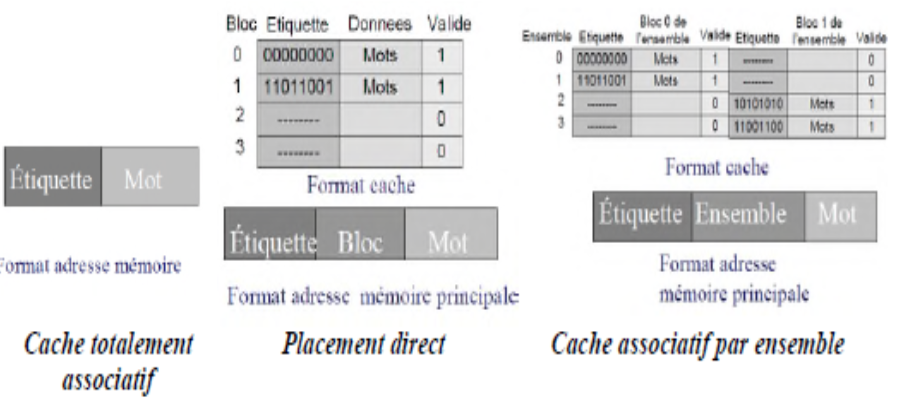

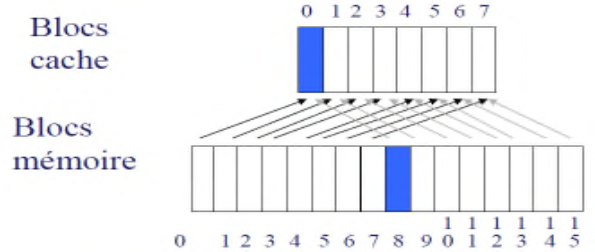

1- Cache purement associatif (Fully Associative)

Chaque bloc mémoire peut être placé dans n'importe quel bloc du cache.

L’avantage de l’adressage complètement associatif est qu’il très souple et efficace pour gérer les lignes de manière optimale en terme de succès d’accès. En général, le taux de succès est de l’ordre de 90 à 95%.

Cependant, dans ce type d’adressage, on doit, au pire cas, parcourir toutes les lignes du cache pour savoir si la ligne cherchée s’y trouve ou pas.

2- Cache purement direct (Direct mapped)

Le cache direct représente le type d’adressage le plus simple. Dans ce type d’adressage, il y a un emplacement réservé pour chaque ligne mémoire. L’emplacement dans la mémoire cache à déterminé à partir du numéro de ligne mémoire en prenant le numéro de la ligne modulo le nombre de lignes dans le cache. Calcul de l’emplacement (Numéro de ligne) = (Adresse du bloc) MOD (Nombre de lignes dans la cache).

Ce type d’adressage a deux avantages importants :

- On sait immédiatement où aller chercher la ligne.

- Accès très rapide à la ligne (avec une latence d’un cycle d’horloge)

Cependant, ce type d’adressage souffre de quelques inconvénients comme par exemple :

- On peut parfois arriver à décharger et charger souvent les mêmes lignes alors que d’autres lignes sont peu accédées.

- Peu efficace en pratique. Taux de succès entre 60 et 80 %.

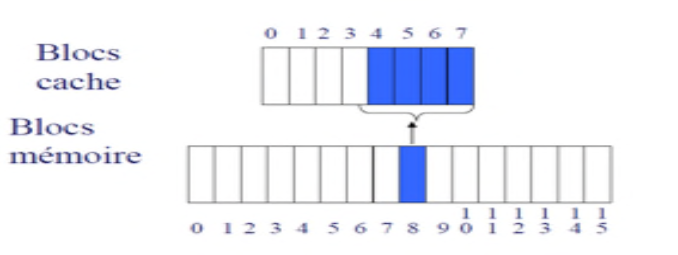

3- Cache

associatif par ensemble (Set Associative)

Lignes sont groupées en ensembles. Au lieu d’affecter un bloc de la mémoire centrale à une seule ligne de cache, il est d’abord affecté à un ensemble. Le bloc peut être placé dans n’importe quelle ligne de l’ensemble correspondant.

Calcul de l’emplacement : (Numéro de l’ensemble) = (Adresse du bloc) MOD (Nombre d’ensembles)

Ce type d’adressage possède beaucoup d’avantages, par exemple :

- Plus souple et efficace que la correspondance directe. Taux de succès de 80% à 90%.

- Temps d’accès très court = 2.5 cycles pour N = 4.

- C’est la méthode utilisée en pratique car elle garantit un meilleur compromis.

Exercice : Pentium 4 Prescott ayant les caractéristiques de mémoire cache suivantes :

- L1 (données) : 16 Kbits ; lignes de 64 bits ; associative par ensembles de 8

- L2 : 1 Mbits ; lignes de 128 bits ; associative par ensembles de 8

1- Combien y-a-t-il de lignes dans cette mémoire cache ?

2- Combien y-a-t-il de blocs associatifs dans cette mémoire cache ?

Solution :

1- Combien y-a-t-il de lignes dans cette mémoire cache ?

Nombre de lignes L1 = Taille cache / Taille de la ligne = 16 Kbits / 64 bits = 24 * 210 / 26 = 28 Lignes

Nombre de lignes L2 = Taille cache / Taille de la ligne = 1 Mbits / 128 bits = 220 / 27 = 213 Lignes

2- Combien y-a-t-il de blocs associatifs dans cette mémoire cache ?

Nombre de blocs L1= Nombre de lignes/ Nombre de lignes par bloc = 28 / 8 = 25 blocs

Nombre de blocs L2= Nombre de lignes/ Nombre de lignes par bloc = 213 / 8 = 210 blocs

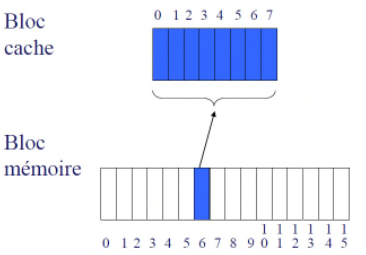

4. Accès à un bloc du cache

Les adresses mémoires peuvent être construites en fonction de la correspondance entre mémoire principale et cache. Dans ce cas, l'adresse mémoire d'un mot contient des informations sur sa présence dans un bloc et sa présence éventuelle dans le cache. Elle se décompose en deux parties :

- Un numéro de bloc,

qui se décompose en

- un index, correspondant à l'emplacement de e bloc dans le cache

- une étiquette permettant d'identifier le bloc mémoire correspondant au bloc placé dans le cache

- Un déplacement dans le bloc (le numéro du mot dans le bloc).

Ainsi, une table d'étiquette est maintenue, ce qui donne pour chaque bloc du cache l'étiquette du bloc mémoire placé dans ce bloc, ou le fait qu'aucun bloc mémoire n'a été copié dans ce bloc.