## TD 1

### Exercice 1 :

Un bus d'adresses constitué de 16 bits. Les bits de ce bus sont repérés de  $A_{15}$  à  $A_0$ .

- 1) Calculer le nombre d'adresses possibles.

- 2) Déduire en octets la capacité de la mémoire dans le cas où un mot mémoire est de 32 bits (4 octets).

### Exercice 2 :

- 1) Quelle est la taille de la mémoire centrale en octets dont la taille du registre RA est de 16 bits et dont les mots mémoires sont de 16 bits ?

- 2) Si la taille de la mémoire centrale est égale à 512 KO sachant que l'octet est adressable, quelle est la taille du registre d'adresse ?

### Exercice 3 :

Si le registre d'adresse comporte 32 bits, calculer :

- 1) le nombre de mots adressables si un mot = 1 octet.

- 2) la taille de la mémoire en MO en GO.

- 3) le nombre de mots adressables si un mot = 4 octets.

- 4) la taille de la mémoire pour ce dernier cas.

- 5) quelle est la plus haute adresse dans chaque cas.

### Exercice 4

Lesquelles de ces organisations mémoires sont possibles, impossibles ? Lesquelles vous semblent raisonnables, pourquoi ? Calculer la taille de la mémoire correspondante en Ko.

- 1) 10 bits d'adresse, 1024 mots et 8 bits par mot

- 2) 10 bits d'adresse, 1024 mots et 16 bits par mot

- 3) 9 bits d'adresse, 1024 mots et 8 bits par mot

- 4) 11 bits d'adresse, 1024 mots et 16 bits par mot

- 5) 10 bits d'adresse, 16 mots et 1024 bits par mot

### Exercice 5

Soit une architecture de Von Neumann munie d'une mémoire de 2048 K mots de 16 bits.

- 1) Donner la taille d'un mot mémoire.

- 2) Donner le nombre de mots mémoire.

- 3) Donner la capacité de cette mémoire en MO et GO.

- 4) Sur cette mémoire on veut stocker un tableau. Sachant que chaque élément du tableau est représenté par 32 bits. Calculer en hexadécimal (base 16) l'adresse du premier élément (1<sup>er</sup>) sachant que le dixième élément (10<sup>ième</sup>) est stocké à partir de l'adresse  $F0_{(16)}$ .

### Exercice 6

On désire réaliser une mémoire de 2048 mots de 16 bits.

- 1) Quelle est la taille du bus d'adresses ?

- 2) Quelle est la taille du bus de données ?

### Exercice 7

On veut réaliser une mémoire de 1KO (la taille d'un mot est de 8 bits) en utilisant des boîtiers de taille 256 mots de 4 bits) ?

### Exercice 8

Réaliser trois schémas de mémoires de 2 Méga-octets en utilisant des circuits de :

- a) 512 kilo-mots de 8 bits.

- b) 2048 kilo-mots de 4 bits.

- c) 256 kilo-mots de 4 bits.

### Exercice 9

Faire le schéma d'une mémoire de  $2048 \times 8$  à l'aide de boîtiers de  $256 \times 8$  avec un degré d'entrelacement  $d=4$ .

### Exercice 10

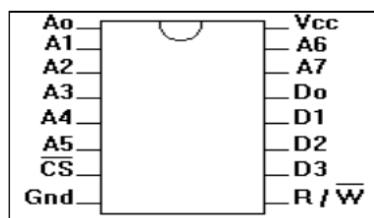

On veut réaliser une mémoire de 4096 mots de 4 bits organisée en 2 modules avec un degré d'entrelacement  $d=4$  à l'aide du boîtier suivant :

A0-A7: Bus d'adresses. D0-D3: Bus de données.

Représenter schématiquement un des 2 modules en détaillant toutes les connexions.

### Exercice 11

On veut réaliser une machine dont le bus d'adresses est sur 34 bits et le bus de données sur 64 bits. On dispose de mémoires de 1 Giga mots de 64 bits.

Donner le schéma de la mémoire, qui est décomposé en 4 modules entrelacés (l'entrelacement se fait à l'intérieur de chaque module et il est de degré  $d=4$ ). Représenter toutes les connexions nécessaires.