Chapter II

Interrupts

II-1 Processor state

II-1-1 Instruction and program

The actions performed by a processor consist of sequence of elementary actions defined by an instruction set for a given processor. The program is a series of instructions.

By convention, the state of a processor and its environment is not defined during the execution of an instruction. The processor and its environment are only observable at the instant separating the execution of two instructions (observable point).

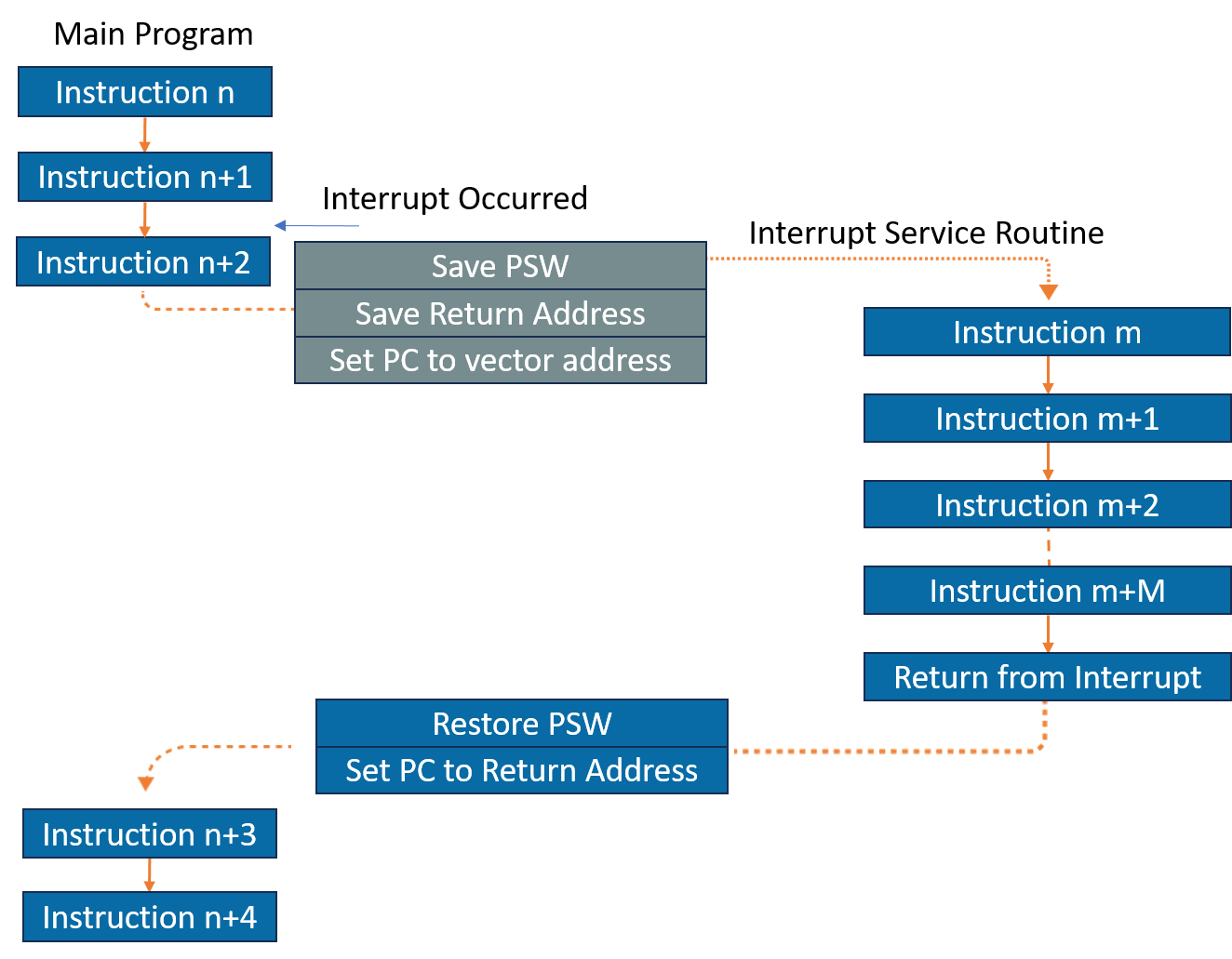

Figure 10: Processor Execution Cycle

All instructions take place in four steps:

- searching for instructions in memory (FETCH),

- instruction decoding (DECODE),

- execution of the instruction (EXECUTE),

- the transition to the next instruction (NEXT).

II-1-2 Information of state

The state of a processor is defined by the values of a set of registers that are part of it. We can distinguish two kinds:

- Programmable registers, which can be explicitly designated as operands in an instruction.

- Internal registers which cannot be designated, but which are implicit operands in certain instructions.

The set of internal registers is commonly grouped into a single piece of information called Processor Status Word (PSW).

The content of the status word depends on the processor type, it contains the following information concerning:

- the execution state of the program being interpreted by the processor,

- the definition of the processor environment and the permitted actions.

State of execution of program

The processor may be in a waiting state where no programs exist. Otherwise, the execution state of a program, at an observable point, is defined by:

- the address of the next instruction to be executed (program counter),

- the current value of the condition code,

- the contents of the programmable registers (which are not part of the status word).

A processor can only go from the waiting state to the active state following an interrupt.

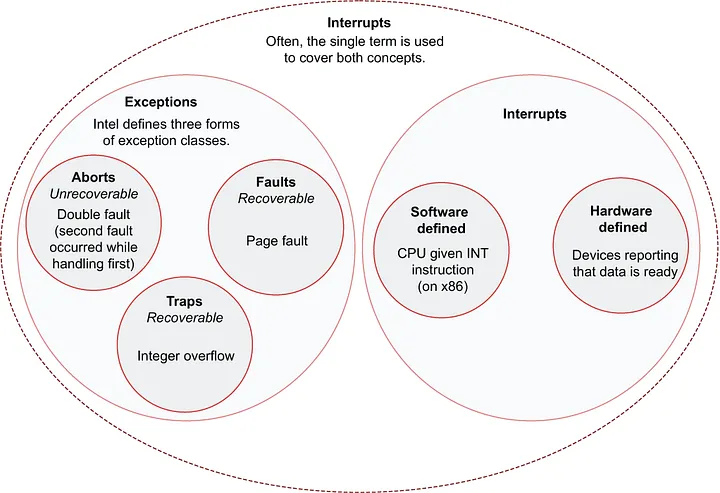

II-2 Mechanism of CPU State switching

The state switching mechanism allows in an indivisible operation:

- to store the contents of the PSW in a specific memory location and

- to load into the PSW new content prepared in advance in a specific location in the memory.

This change of state is only possible if the processor is in an interruptible point (between the execution of two instructions, waiting state and for certain very long instructions at intermediate points).

Figure 11: Mechanism of CPU state switching

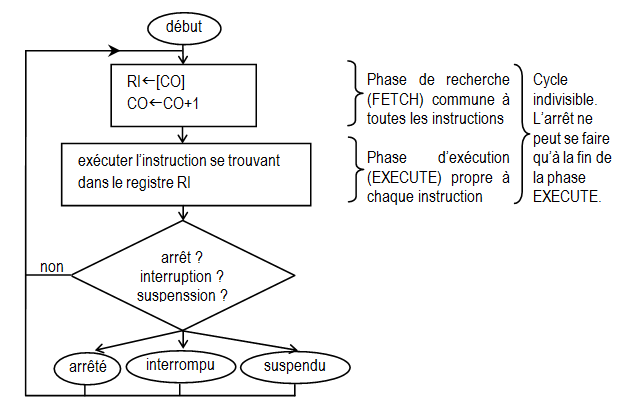

II-3 Interrupt, trap and SVC

The switching of state is only possible if the processor is at an observable point. This change is triggered following the state of an indicator consulted by the processor after the execution of each instruction. The indicators are distinguished according to their meanings and the way in which they are modified.

We have the following cases:

II-3-1 Interrupts

When a state switching indicator is changed from outside the processor, it is said to be an interrupt.

This modification can be made by another processor, by a human operator and more generally by any physical process taking place outside the interrupted processor (end of I/O, mouse click, keyboard typing, clock, etc.).

An interrupt forces the processor to suspend, at the first interruptible point, the execution of the current program and to execute a specific program (the interrupt program) with a switching of state.

A processor can be interrupted by various causes. The interrupt mechanism must make it possible to distinguish these causes. Two basic schemes are possible:

- a separate indicator is associated with each cause of interruption (we often speak of interrupt level). Each level is associated with a distinct pair of locations for saving and loading the PSW. In other words, each level corresponds to a distinct processing program automatically activated by the interrupt mechanism.

- a single flag is used for all interrupts with a unique pair of locations for saving and loading the PSW. Additional information (interrupt code, contained in the PSW or in a conventional memory location) makes it possible to distinguish between possible causes. The first task of the interrupt program is to consult this code to determine the origin of the interrupt and call the appropriate routine.

Interrupt priority

When there are multiple levels of interruption, it is possible that two indicators corresponding to two distinct causes are modified at the same time. The conflict is resolved by prioritizing the interrupt levels.

This order can be set once and for all or modifiable.

Sometimes, it is useful to protect the execution of a sequence of instructions against certain interruptions (for example the interrupt programs themselves).

This is possible by delaying the state switching caused by the modification of the indicator. We then say that the level is masked or inhibited.

Removing inhibition (unmasking) authorizes the state switching.

Information about the maskable/unmaskable interrupt levels is contained in PSW. The interrupt levels thar are never maskable called NMI: Not Maskable Interrupt.

We can completely remove and not only delay the effect of any change in the indicator of a certain interrupt level. Everything happens as if the cause itself of the interruption was removed. The interrupt level is said to be disarmed; the level can be rearmed (returned to service).

Note: Arming, disarming, masking, unmasking and interrupt triggering operations are always carried out by privileged instructions.

II-3-2 Trap

When a state change indicator is modified by a cause linked to the execution of an instruction in progress, we say that there is a trap. The role of the trap mechanism is essentially to deal with an anomaly in the progress of an instruction.

For example

- incorrect data (arithmetic overflow, division by zero, etc.)

- attempt to execute an operation prohibited by a protection device (memory violation, execution of a privileged instruction in slave mode)

Note: Given the synchronous nature of the trap (associated with instructions in progress) the notion of masking does not make sense. A trap can be removed but not delayed.

II-3-3 System call

A System Call or SuperVisor Call (SVC) is an instruction whose function is to cause the processor state to switch. A call to the system causes the execution of a specified program with a processor state change and saves the processor state at the time of the call.

This instruction is mainly used to make the call from a user program executed in slave mode. For example, file access functions (open, read, close, etc.)

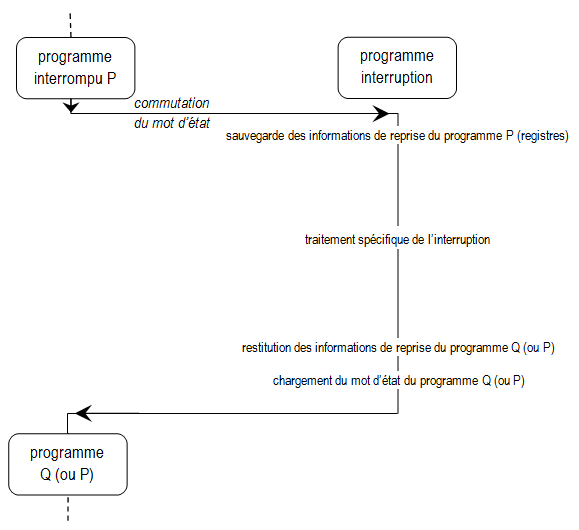

II-4 General diagram of an interrupt program

The function of an interrupt is to force a processor to react to an event. Execution of the current program is suspended, and an interrupt program is executed. The program then resumed by the processor may be the interrupted program or another.

Figure 12: General diagram of an interrupt program